2025/02/24

604

为什么低电压MOSFET在电力电子系统中被广泛应用? - pcim电力展

2025PCIM Asia Shanghai — 上海国际电力元件、可再生能源管理展览会暨研讨会将行于9月24日至9月26日在上海新国际博览中心举行,邀您关注今日上海电子展新资讯:

根据全球技术研究和咨询公司Omdia的数据,2023年全球分立功率MOSFET市场(涵盖从几十伏到1700伏的器件)价值约为111亿美元,预计到2028年将达到约125亿美元,复合年增长率(CAGR)为2.4%。这些数据不包括硅保护MOSFET。

从电压细分来看,可以确定两个低电压子范围:

≤40 V,2023年市场价值为44亿美元,预计到2028年增长至48亿美元(CAGR = 1.5%)

41 V至200 V,2023年市场价值为38亿美元,预计到2026年增长至45亿美元(CAGR = 3.6%)

在全球范围内,低电压MOSFET占据了MOSFET市场总量的74%,主要得益于其在汽车、数据中心、计算和消费电子等关键领域的强劲表现。随着智能手机、笔记本电脑、可穿戴设备和便携设备的广泛普及,市场对节能组件的需求不断增加,以确保电池寿命长和高效的电源管理。此外,电子设备小型化的需求进一步推动了紧凑高效封装的发展。

低电压技术

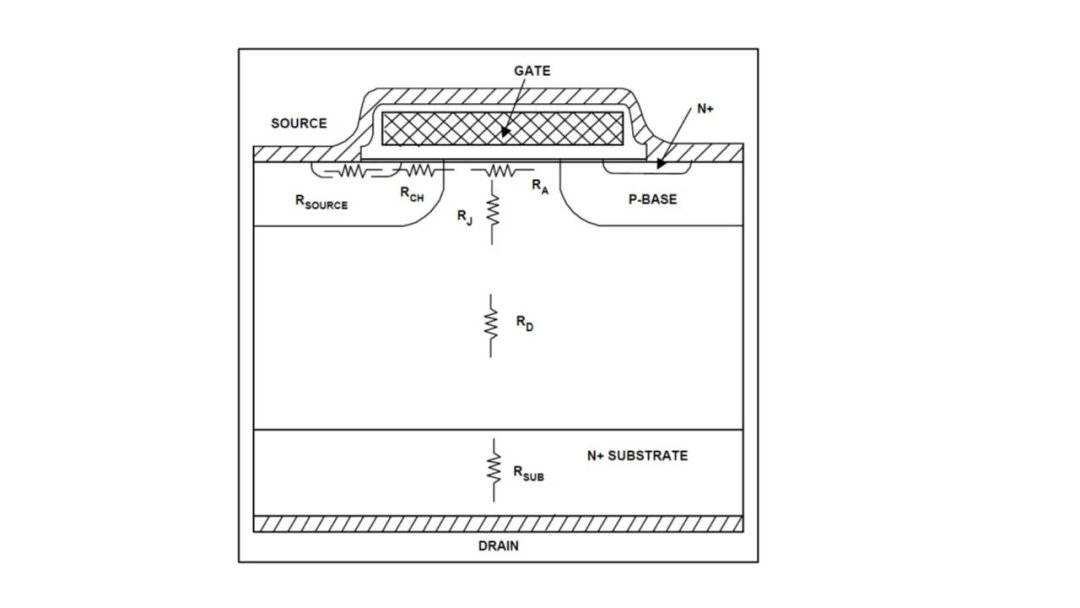

与N沟道MOSFET相比,P沟道MOSFET的市场份额相对较小,低电压的主流技术是沟槽栅极技术。该技术旨在克服早期平面结构在提供更低导通电阻和更低损耗方面的局限性。通过在彻底蚀刻的沟槽区域中插入栅极结构,这些MOSFET在低于200 V的电压范围内实现了导通电阻的改善,这得益于沟道电阻和JFET电阻的降低。图1展示了垂直平面MOSFET内部的主要电阻成分,其中导通电阻是各部分贡献的总和。

图1

图1

英飞凌的OptiMOS产品系列

在最近的一次网络研讨会上,英飞凌展示了采用源极向下(S-d)封装的OptiMOS功率MOSFET系列。该公司的低电压产品组合在新的行业标准封装中提供了前所未有的高功率密度。该系列产品旨在满足脱碳和数字化日益严格的要求。为应对这些全球趋势,英飞凌专注于三个增长领域:绿色能源、清洁安全出行和智能安全物联网。其中,电力系统的核心竞争力至关重要,包括控制器、驱动IC和功率开关,这些领域不仅需要广泛的技术组合,还需要软件和算法技能。

英飞凌的低电压产品系列由两个产品家族组成:通用型StrongIRFET,涵盖20 V至300 V的电压范围,面向价格敏感的核心和大众市场;以及OptiMOS,满足高性能要求,具有最佳的“导通电阻×栅极电荷”品质因数和功率密度,且不牺牲竞争力。后者涵盖15 V(OptiMOS 7)至300 V的电压范围,具体取决于产品迭代或代际。

数据中心需要更高效的MOSFET

在硅技术和封装方面需要彻底改革的关键应用之一是数据中心和人工智能,这主要受到生成式聊天机器人、自动驾驶、车对车通信等技术的推动。预计到2030年,数据量将以30%的复合年增长率(CAGR)显著增加。例如,2010年至2025年间,生成、传输和存储的数据预计将增加146倍,达到180泽字节(180 × 10²¹字节)。如果这些数据存储在蓝光光盘上,其堆叠高度将相当于地球到月球距离的23倍。

估计数据中心的功耗将随着数据处理需求的激增而增加,如果这些能源需求由化石燃料满足,将对环境产生重大影响。根据国际能源署的数据,2022年数据中心的电力消耗(约2500亿千瓦时)超过了西班牙等国家的用电量。按当前速度,到2030年,数据中心将占全球总电力需求的4%。

通过结合新型功率半导体技术(包括SiC和GaN)、创新封装(多芯片嵌入、模块、集成磁性元件)、新颖的系统架构以及智能控制和软件,可以实现显著的效率提升。

源极向下封装

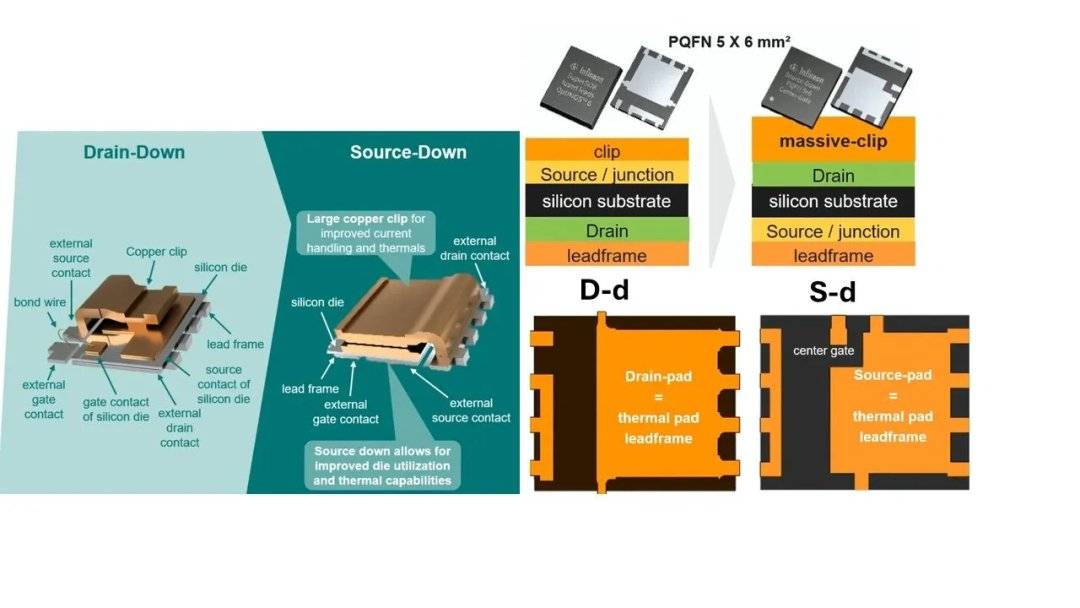

新的S-d封装是优化硅设计和封装技术的成功范例,旨在提供符合新兴应用严格功率要求的创新产品。图2以3D形式总结了S-d解决方案与传统漏极向下(D-d)解决方案的特点。在新概念中,硅芯片被倒置,源极电位连接到引线框架,而不是漏极电位。

首先,S-d布局采用更大的铜夹,可以容纳更大的芯片,具有更低的导通电阻、更好的热性能和更高的电流承载能力,从而实现显著更高的功率密度。此外,在S-d中,硅芯片的栅极不再通过键合线连接,而是直接键合到引线框架,这有助于提高电气性能并减少寄生电感。此外,与仅使用底部冷却和散热器的模压封装相比,双面冷却(DSC)封装可以散发3倍以上的功率。

图2

图2

其他优势包括最小化PCB空间和损耗,以及由于漏极到源极爬电距离的增加,可以将栅极放置在中心位置(而不仅仅是角落位置),从而更容易实现多个开关的并联——这些要求在空间受限的应用中至关重要。改进可以通过结温与漏极电流的对比图来量化,基准测试在5×6 mm PQFN封装中进行,结果显示:

在给定结温下,S-d比D-d多提供11%的电流,或

在相同电流下,新封装的外壳温度比D-d低30%。

进一步优化PCB布局

这两种封装选项可以在半桥拓扑中结合使用,从而显著优化PCB设计。在这种配置中,高侧晶体管(T1)采用D-d封装,而低侧晶体管(T2)采用S-d封装。其优势如下:

T1为VIN连接提供了大面积的铜(Cu)区域和热通孔,而T2为GND端子提供了同样大的Cu区域和热通孔,使设计人员能够显著优化热管理。

相比之下,较小的相位节点区域减少了层间的电容耦合,从而改善了EMI响应。

最后,S-d相对于D-d的更大爬电距离(0.75 mm对0.59 mm)允许适当的栅极布线,因为可以将栅极放置在MOSFET的另一侧,而无需使用其他层。

PQFN DSC S-d

大而厚的铜夹可以暴露出来,形成热垫并实现DSC;此功能适用于5×6 mm和3.3×3.3 mm版本。与仅使用底部冷却和散热器的模压封装相比,DSC封装可以提供4倍的散热能力。这也允许更高的电流通过开关。

服务器应用示例

在服务器应用中,电力从电网开始,提供220 VAC,通过离线电源转换为48 VDC;DC/DC转换包括两个阶段,将电压从48 V降至12 V,再从12 V降至约1 V,或GPU或高性能处理单元所需的任何电压。为了进行比较,使用了8:1转换比的中间总线转换器(IBC 8:1)。

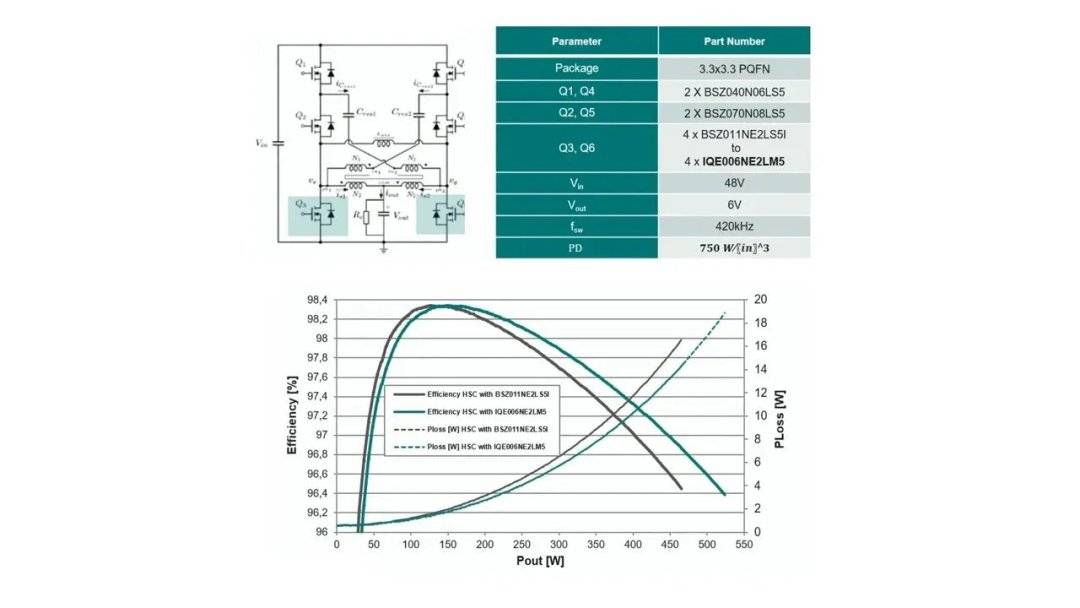

图3

图3

图3显示了电路拓扑,其中晶体管Q1、Q2、Q4和Q5在两次测试中保持不变,而Q3和Q6在一个案例中采用D-d封装,在另一个案例中采用S-d封装。图中还显示了使用的器件及其效率和损耗曲线。总的来说,在450 W输出功率下,S-d比D-d运行温度低9°C。也可以说,在相同温度下,S-d比其“竞争对手”封装多提供6%的功率。

文章来源:浮思特科技

2025PCIM Asia Shanghai — 上海国际电力元件、可再生能源管理展览会暨研讨会将于2025年9月24日至9月26日在上海新国际博览中心举行;上海电子展更多资讯,详情请登陆官网 https://pcim.gymf.com.cn

| 凡本网注明“来源:广州光亚法兰克福展览有限公司”的所有作品,版权均属于广州光亚法兰克福展览有限公司,转载请注明。 凡注明为其它来源的信息,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点及对其真实性负责。若作者对转载有任何异议,请联络本网站,联系方式:020-38217916;我们将及时予以更正。 |

欢迎莅临:PCIM Asia Shenzhen — 深圳国际电力元件、可再生能源管理展览会暨研讨会!

电力电子、智能运动、可再生能源、能源管理

主办单位官方微信