2024/08/12

1592

先进封装Chiplet技术 - 电力元件展

2024深圳国际电力元件、可再生能源管理展览会将行于8月28日至8月30日在深圳国际会展中心(宝安新馆)举行,邀您关注今日深圳电子展新资讯:

摘要:随着先进制程技术迭代到5nm、3nm,摩尔定律的效应逐渐趋缓,制程开发成本和复杂度也在不断攀升。在芯片散热、传输带宽、制造良率等面临挑战的背景下,单颗芯片的性能提升遇到了“功耗墙、存储墙、面积墙”等瓶颈。而Chiplet技术的出现,为这一问题提供了新的解决思路。本文概述Chiplet芯片的底层封装技术,阐述我国先进封装领域发展的现状,对我国先进封装发展提出建议。

0 引言

随着先进制程迭代到5nm、3nm,摩尔定律逐渐趋缓,先进制程的开发成本及复杂度日益提升。受芯片散热能力、传输带宽、制造良率等多种因素共同影响,芯片发展遇到了“功耗墙、存储墙、面积墙”等瓶颈,限制了单颗芯片的性能提升[1]。而Chiplet能在不改变制程的前提下,先将不同厂家、不同制程的Die(裸片)通过Die-to-Die内部互联技术制造成Chiplet(“芯粒”),再通过先进封装技术将Chiplet集成制造为“系统芯片”,实现一种新形式的IP复用。Chiplet先进封装可以提供更低的功率、更高的带宽、更低的成本和更灵活的形状因子,打造出性能更强的高算力芯片产品。

1 Chiplet技术的优势

Chiplet芯片设计相对于传统的集成电路单芯片(System on Chip,SoC)设计可实现如下突破。

(1)通过芯粒级的IP复用/芯粒预制组合,实现芯片的敏捷设计。由于芯粒可以独立设计和组装,制造商可以根据特定需要选择不同类型、不同规格和不同供应商的芯粒进行组合,很大程度上提高了芯片设计的灵活性和可定制化程度,不仅能满足场景应用的“碎片化”需求,而且显著缩短芯片的上市时间[2]。

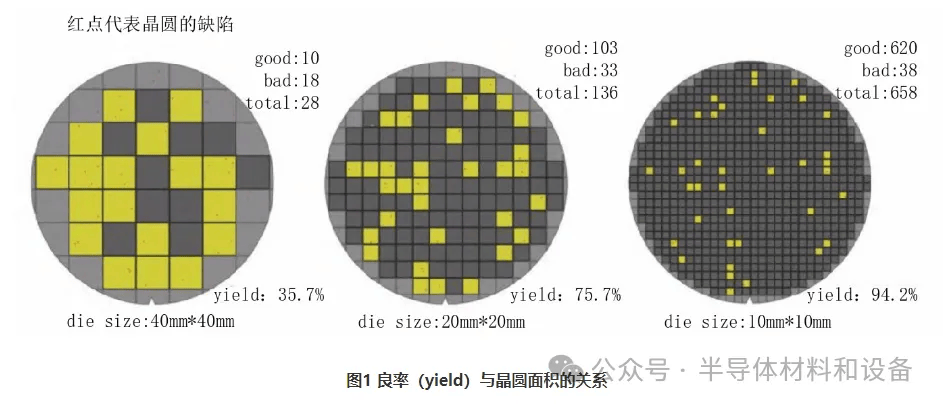

(2)更小的芯粒尺寸,带来更高的良率,降低制造成本。伴随高端芯片性能的快速提升,集成电路单芯片中的晶体管数量也在快速增加,导致芯片面积不断变大。就晶圆制造工艺而言,芯片面积越大,工艺的良率越低。而Chiplet技术通过将大芯片拆解分割成几颗小芯粒,使得失效点落在单个小芯粒上的概率大大降低,如图1所示,由此集成的大芯片可以实现制造面积的突破和良率的提升,制造成本大幅降低。

(3)不同芯粒可采用不同的工艺制程,突破单一工艺的局限。Chiplet芯片架构下,负责不同功能的芯粒不再需要迭代至统一的工艺制程,而是可以将最佳节点实现的不同芯粒进行混合集成,也就是可对芯片的不同IP单元进行选择性迭代,迭代的部分Die还能用于制作下一代产品,不仅摊薄单次工程费用,更大幅缩短了产品上市周期。例如,可以将传统的电子芯片与光电子器件集成在同一芯片上,实现光电混合芯片。这种光电混合芯片结合了电子和光子的优势,可以在高速数据传输、光通信、光计算等领域发挥重要作用[3]。

2 先进封装技术

Chiplet技术发展的基础是先进封装技术,尤其在芯片尺寸不断增大且架构更加复杂的情况下。为了高效地整合多颗芯片,需要采用2.5D和3D封装技术,这些技术目前由Intel、台积电和日月光等公司主导[4]。为了明晰支持Chiplet芯片的底层封装技术,本文对其进行了分类梳理。

2.1 CoWos(Chip-on-Wafer-on-Substrate)

Co Wo S是台积电主导的2.5D封装技术,先将多颗芯粒(Compute计算芯粒、HBM内存芯粒等)通过Chip on Wafer(CoW)的封装制程连接至硅中介层(Silicon Interposer),再与底层基板连接,整合成CoWoS[5]。

相较于传统的2D Sip(System-in-Package)封装,2.5D封装在Sip基板与芯片之间,插入硅中介层,并以硅穿孔(TSV,Through-Silicon Via)连接上下的金属层,克服了Sip基板难以高密度布线而限制封装密度的难题,并达到了更低互联延时、更高互联带宽、引脚少的效果。CoWoS技术的局限性在于,由于中介层的尺寸限制(2倍掩膜版尺寸),可以提供的封装密度相对有限,并且硅中介层的引入带来额外的制造成本和更高的技术复杂度,以及随之而来的整体良率降低。

2.2 EMIB(Embedded Multi-Die Interconnect Bridge)

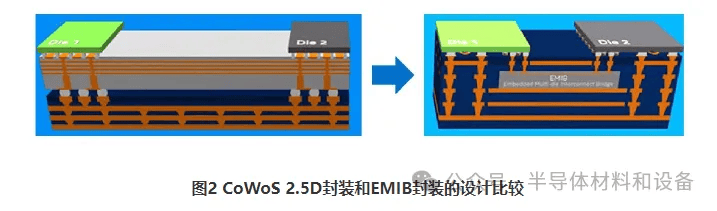

EMIB是Intel主导的2.5D封装技术,使用多个嵌入式包含多个路由层的桥接芯片,同时内嵌至封装基板,达到高效和高密度的封装,如图2所示。相较于Co Wo S封装技术,由于EMIB没有使用中间介质层,可以去掉原有连接至Interposer所需的TSVs,且不受中介层尺寸所带来的封装尺寸限制,因此设计更简洁,实现更低的成本、更高的集成度以及更高的制造良率。EMIB技术的局限在于,EMIB技术需要封装工艺配合桥接芯片(EMIB),其技术门槛和复杂度更高。

2.3 3D封装技术

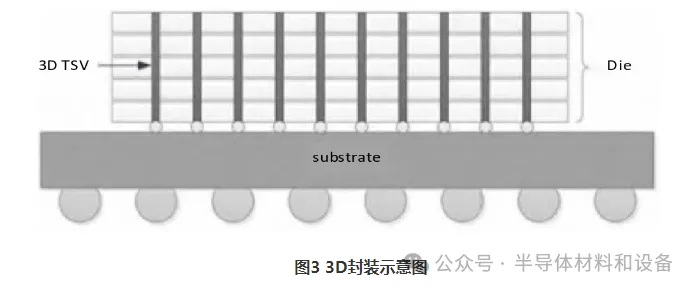

3D封装技术可以实现3DIC,即芯粒之间的堆叠和高密度互联,如图3所示,从而在三维空间中实现更高的性能和算力密度。同时,3D封装技术难度更高,目前只有Intel和台积电掌握并商用这种技术。

使用有源中介层的3D封装方式是将先进工艺实现的计算芯片堆叠在大工艺节点制造的基底芯片上,计算芯片和基底芯片通过TSV互连,同时计算芯片之间的通信通过基底芯片中的互连实现[6]。基于此,设计人员可在新的产品形态中融入不同的技术专利模块与各种存储芯片和I/O配置,使得产品能够分解成更小的“芯片组合”。

从最新3D封装技术落地进展来看,Intel Lakefield采用3D Foveros封装技术,而台积电的3D封装技术So IC按原计划在2023年实现量产,三星的3D封装技术已应用于7nm EUV芯片。以Intel第1款CPU混合架构产品Lakefield为例,高性能运算芯片采用10nm实现,基底硅片采用22nm实现,集成了CPU处理器、GPU核心显卡、内存控制器、图像处理单元、显示引擎以及各种各样的I/O、调试和控制模块[7]。最后这颗芯片的尺寸长宽只有12mm×12mm,高度仅1mm,待机功耗2mW,是一款典型的面向超算的高性能超算处理器芯片。

然而,先进封装并不是越新的技术越好,在一些应用场景下,若先进封装的价格过高,甚至超过了晶圆的成本,其将难以大范围、大规模地投入量产。提高良率、降低成本是目前国内封装厂的首要任务。对此,2023年8月底台积电将2.5D和3D先进封装相关技术整合为3DFabric平台[8,9]。

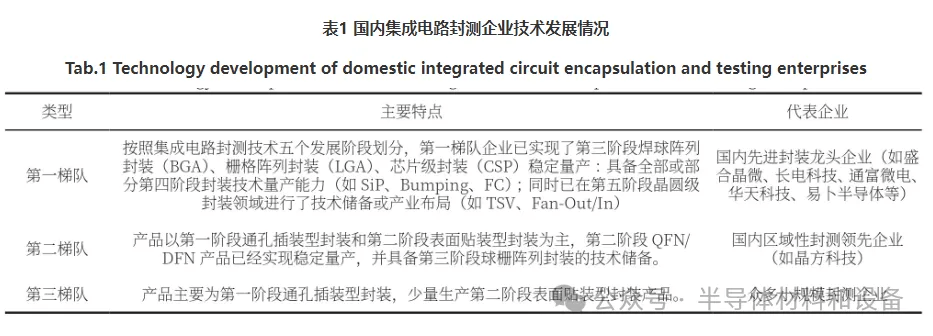

我国本土情况:按照技术储备、产品线、先进封装收入占比等指标,本文将国内集成电路企业大致分为3个梯队,3个梯队的主要特点及代表企业如表1所示。

3 我国先进封装技术存在的问题

半导体封装属于半导体制造工艺的后道工序,本土封装厂对于Chiplet大芯片的架构设计认知不足,在Chiplet系统设计方面存在技术缺口。尽管Chiplet芯片的技术关键在于先进封装,但本土封装厂难以作为牵头方引领产业链升级。

先进封装关键装备及材料尚未实现自主可控。支撑我国封装产业链发展的整体基础技术水平不高,先进封测技术所需的关键封装、测试设备和材料主要依赖进口,难以满足市场需求。

4 先进封装Chiplet技术发展的建议

结合Chiplet方案,2.5D/3D高级封装技术的快速发展,将为芯片设计打开一扇新大门[10]。从现阶段技术成熟度角度分析,尽管美国企业起步早,技术相对领先,但因为Chiplet技术总体上仍处于发展演进阶段,尚未形成技术垄断壁垒,因此中国依然有较大的机会,建议如下。

(1)成立产业联盟。由政府作为牵头方,成立Chiplet技术产业联盟,从而促进产业链上下游企业的协同创新,共享技术和资源,降低研发成本,加快技术创新。

(2)政策支持。政府可以出台相关政策,为产业联盟提供资金和资源支持。例如采用“前资助”与“后补助”模式,为产业联盟提供专项资金、税收优惠、设计公司流片补助等政策,降低企业研发成本和风险。

(3)培养专业人才。封装技术需要专业的人才支持,包括工程师、技术专家和研究人员等。加强人才培养,提高人才素质,可以为封装技术的发展提供有力的技术支持。

(4)加强标准化。封装技术需要遵循一定的标准和规范,以确保产品的兼容性和可靠性,促进技术的推广和应用。

5 结语

随着摩尔定律逐渐接近物理极限,单纯依靠工艺升级获得芯片性能提升和成本下降的路线已经露出疲态,而Chiplet技术被认为是“后摩尔时代”半导体技术发展的重要方向。在我国,已有一些公司紧跟市场需求和技术趋势,积极探索Chiplet技术,然而,与国际先进水平相比,我国在技术研发、产业链建设等方面仍需进一步加强,以推动Chiplet技术的广泛应用和产业发展。需要注意的是,随着生成式AI、自动驾驶、大数据等下游应用的爆发,高算力芯片的市场需求不断增长,进而带动先进封装加速渗透与成长。因此,我国在先进封装Chiplet技术方面仍有巨大的发展潜力和市场空间。

文章来源:半导体材料和设备

2024深圳国际电力元件、可再生能源管理展览会将于2024年8月28日至8月30日在深圳国际会展中心(宝安新馆)举行;深圳电子展更多资讯,详情请登陆官网 https://pcim.gymf.com.cn

扫码实名预约,领取入场证!

| 凡本网注明“来源:广州光亚法兰克福展览有限公司”的所有作品,版权均属于广州光亚法兰克福展览有限公司,转载请注明。 凡注明为其它来源的信息,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点及对其真实性负责。若作者对转载有任何异议,请联络本网站,联系方式:020-38217916;我们将及时予以更正。 |

欢迎莅临:PCIM Asia Shenzhen — 深圳国际电力元件、可再生能源管理展览会暨研讨会!

电力电子、智能运动、可再生能源、能源管理

主办单位官方微信