2022/10/26

774

CMOS电路的功耗分析 - 上海电力电子展

2023上海国际电力元件、可再生能源管理展览会将行于8月29日至8月31日在上海新国际博览中心举行,邀您关注今日上海电子展新资讯:

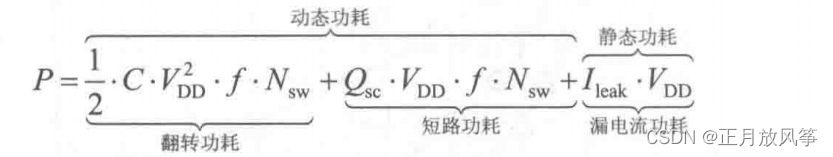

CMOS电路中的功耗由两部分组成。第一部分为负载电容充放电时引起的功耗,称为动态功耗,另一部分为漏电流引起的功耗,称为静态功耗。其中,动态功耗包括翻转功耗和短路功耗。

翻转功耗是数字电路要完成功能计算所必须消耗的功耗,称为有效功耗;

短路功耗是由于CMOS在翻转过程中PMOS管和NMOS管同时导通时消耗的功耗,称为无效功耗。

数字CMOS电路的总功耗如公式所示:

式中,C为结电容,N为单时钟周期内翻转晶体管数目,f为系统工作时钟频率,VDD为供电电压,Qsc。为翻转过程中的短路电量,Ileak为漏电流。

1、动态功耗

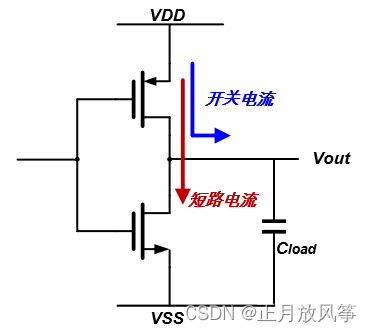

CMOS电路翻转过程中,动态功耗是有翻转电流和短路电流引起的功耗。

当负载电容通过PMOS充电时,电压从0升到VDD,该能量消耗在PMOS器件上,负载电容放电时,电压从VDD降到0,该能量消耗在NMOS器件上。即为翻转功耗。

输入信号从低电平到高电平的变化时间在实际过程中不可能为0,而是有一定的上升或者下降时间,该时间内,导致VDD和VS S之间在短期内出现一条直流通路,此时NMOS和PMOS同时导通,即为短路功耗。

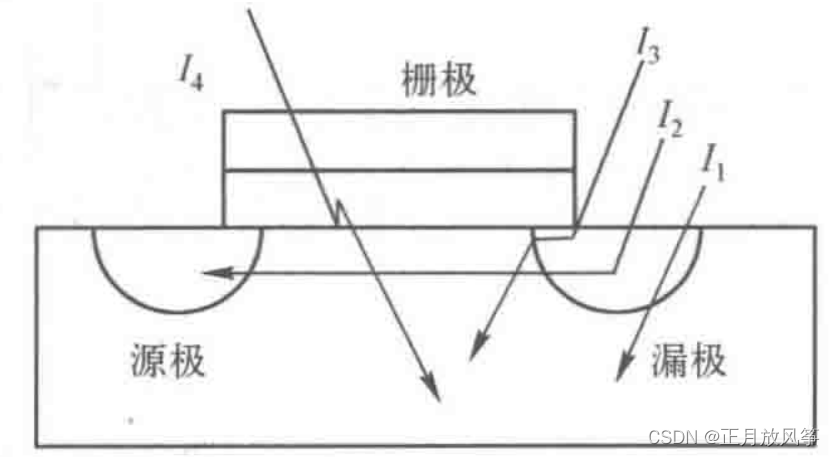

2、静态功耗

静态功耗主要有漏电流引起,有以下几部分组成:

1、PN结反向电流I1

2、源极和漏极之间的亚阈值漏电流I2

3、栅极漏电流,包括栅极和漏极之间的感应漏电流I3

4、栅极和衬底之间的隧道漏电流I4

另一方面,为了满足工作频率越来越高的要求,

就会降低晶体管的阈值电压,使得晶体管能够高速翻转,但是如果阈值电压太低,晶体管不能完全关断,这将产生很大的静态功耗。

随着工艺的进步,晶体管的尺寸变得越来越小,同时带来了更低的工作电压和更大的漏电流。工作电压的降低减小了晶体管的动态功耗,但是由于主频的提高及晶体管数目的增多,系统的总功耗越来越大。由于漏电流的增加,静态功耗在系统总功耗所占比例越来越大。

文章来源:搜狐

2023上海国际电力元件、可再生能源管理展览会将于2023年8月29日至8月31日在在上海新国际博览中心举行;上海电子展更多资讯,详情请登陆官网 https://pcim.gymf.com.cn

| 凡本网注明“来源:广州光亚法兰克福展览有限公司”的所有作品,版权均属于广州光亚法兰克福展览有限公司,转载请注明。 凡注明为其它来源的信息,均转载自其它媒体,转载目的在于传递更多信息,并不代表本网赞同其观点及对其真实性负责。若作者对转载有任何异议,请联络本网站,联系方式:020-38217916;我们将及时予以更正。 |

欢迎莅临:PCIM Asia Shanghai — 上海国际电力元件、可再生能源管理展览会暨研讨会!

电力电子、智能运动、可再生能源、能源管理

主办单位官方微信